Giáo trình CÔNG NGHỆ VI ĐIỆN TỬ - Chương 5 pps

Giáo trình CÔNG NGHỆ VI ĐIỆN TỬ - Chương 5 pps

... Implantation Technique Chương 5 :Công nghệ mạch tích hợp 24 5. 3. Quy tắc layout vi mạch Chương 5 :Công nghệ mạch tích hợp 25 Chương 5 :Công nghệ mạch tích hợp 26 Chương 5 :Công nghệ mạch tích ... transistor p-channel MOSFET Chương 5 :Công nghệ mạch tích hợp 28 Chương 5 :Công nghệ mạch tích hợp 23 5. 2. Các bước chế tạ...

Ngày tải lên: 27/07/2014, 11:21

Giáo trình CÔNG NGHỆ VI ĐIỆN TỬ - Chương 4 pps

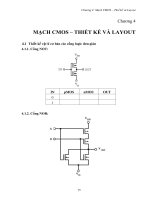

... Chương 4: Mạch CMOS – Thiế kế và Layout 15 Chương 4 MẠCH CMOS – THIẾT KẾ VÀ LAYOUT 4.1 Thiết kế vật lí cơ bản ... 0 1 4.1.2. Cổng NOR: Chương 4: Mạch CMOS – Thiế kế và Layout 17 4.1.4. Cổng XOR: A B P1 P2 P3 P4 P5 N1 N2 N3 N4 N5 OUT 0 0 0 1 ... f. OUT =A.B + C g. FF-D Chương 4: Mạch CMOS...

Ngày tải lên: 27/07/2014, 11:21

Giáo trình CÔNG NGHỆ VI ĐIỆN TỬ - Chương 3 docx

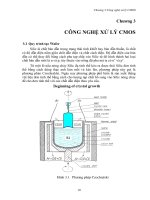

... Chương 3 :Công nghệ xử lý CMOS 10 Chương 3 CÔNG NGHỆ XỬ LÝ CMOS 3.1 Quy trình tạo Wafer Silic là chất bán dẫn trong trạng thái tinh khiết hay bán dẫn thuần, là chất có độ dẫn điện ... die Wafer Chương 3 :Công nghệ xử lý CMOS 13 chu trình nhiệt, nó dùng để dồn tạp chất từ bề mặt silic vào thể tích chung. Nuôi cấy ion bao gồm vi c đưa nền silic tới các nguyên...

Ngày tải lên: 27/07/2014, 11:21

Giáo trình CÔNG NGHỆ VI ĐIỆN TỬ - Chương 2 ppt

... 2 2 .5 0 0 .5 1 1 .5 2 2 .5 x 10 I D (A) VGS= 2 .5 V VGS= 2.0 V VGS= 1 .5 V VGS= 1.0 V Early Saturation Quadratic Relationship 0 0 .5 1 1 .5 2 2 .5 0 1 2 3 4 5 6 x ... cách điện (SiO 2 ) gọi là cổng oxide. Khảo sát 3 kiểu làm vi c của một tụ MOS: Hình 2.4: Sụ tạo kênh truyền n+n+ S G V GS D V DS > V GS - V T V GS - V T +...

Ngày tải lên: 27/07/2014, 11:21